Part 1からPart 5までで検討した内容をこのパートでまとめておきます。

第2層:銅箔(t=35um)

誘電体:FR-4(Er=4.5、t=930um、tanδ= .0004)

第3層:銅箔(t=35um)

誘電体:FR-4(Er=4.5、t=220um、tanδ= .0004)

第4層:銅箔(t=40um)

の寸法でマイクロストリップラインを作ってみて、S11、S21の実測データがあうかどうか、検証してみたいと思います。

Part 1からPart 5までで検討した内容をこのパートでまとめておきます。

Part4で紹介した、グランドビアはL2とL3を接続するだけにしていたのです。これは計算スピードを上げる為なのですが、このような構成を実際のプリント基板で作ろうとすると、とんでもないコストがかかります。

L1からL4へ遷移するマイクロストリップラインのビアには、縦方向に電流が流れるわけですが、この電流の戻り(リターン)を確保するため、その信号ラインビアの近辺にあるグランドにビアを設けることで、周波数特性(S11、S21)が改善することが分かりました。

前回までで、ビアのあるマイクロストリップラインの特性に関するシミュレーションの基本は出来たと思います。

アジレントテクノロジー様(現:キーサイト・テクノロジー様)ご厚意により、パーソナル電磁界シミュレータ、Genesysを使わせていただいています。

アジレントテクノロジー様キーサイトテクノロジー様が開発・販売している「GENESYS」を使った事例を掲載しました。

8月29日に、アジレントテクノロジ社キーサイトテクノロジ様が主催する「50万円台からの高周波シミュレータGENESYS体験セミナ」に参加してきました。

これは何を意味しているかと言うと、テストクーポンの長さ130mmに対してマイクロストリップラインの入り口(Start)から出口(End)までの時間を測定し、実効誘電率を測定しています。画面右のDielectric cがその値です。ここでは「2.16」という値が測定されました。

この条件で計算すると、確かにマイクロストリップラインのインピーダンスは約50オームになるのですが、実効誘電率が大きく違い、GENESYSの計算では、「2.73」とでました。実測値は「2.16」です。

おそらく実測値は間違いないでしょうから、あとはGENESYSに入力するパラメータがおかしいということになります。で、やっぱり気になるのは誘電率です。

誘電率のみを変えても実効誘電率が2.16に近づかなかったため、今度はプリプレグの厚みを、0.25mmから0.2mmにしてみました。すると、実効誘電率が2.16と、実験値に非常に近い値が得られました。

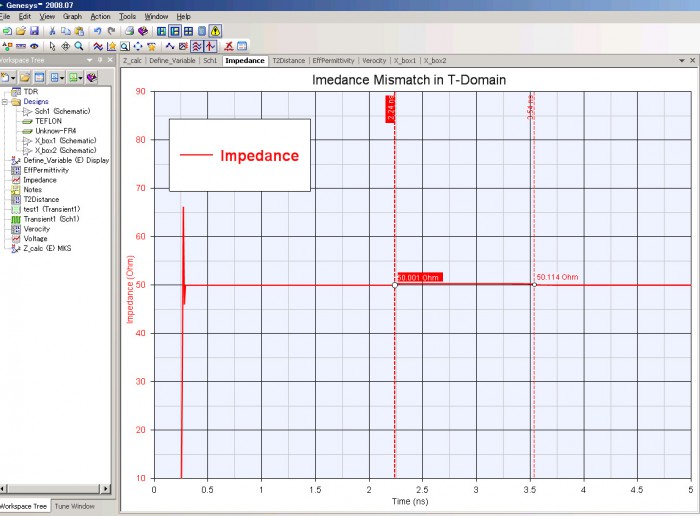

さらにGENESYSのタイムドメイン機能を用いて、最初の図と同じTDR画面を再現してみました。この再現では、コネクタのモデルがありませんので、TDR波形の暴れは再現されません。しかしながら、マイクロストリップラインの上を伝搬する波のスピードは測定することができます。

マイクロストリップラインの条件は、先ほど計算したときと同じで、

マイクロストリップラインの条件は、先ほど計算したときと同じで、

このサイトをオープンしたときにご報告した、1.5Gbps高速シリアル信号回路のデバッグが終了しました。

残念ながら詳細な回路動作に関しては、クライアント様との守秘義務があるので話せませんが、なんとかクライアント様を満足させることができました。

ポイントは、

でしょうか?

特に半田付けプローブ強力なツールとなりました。

この場を借りて、半田付けプローブ、D350STを快く貸し出していただいた、レクロイジャパン株式会社 (現テレダイン・レクロイ・ジャパン)様に厚く御礼申し上げます。

詳細に関しては、以下のエントリーを参照ください。

再製作したプリント基板のMicrostrip Lineは50オーム

半田付けプローブを使ってデバッグを行う(Part 1)

半田付けプローブを使ってデバッグを行う(Part 2)

半田付けプローブで観測した波形