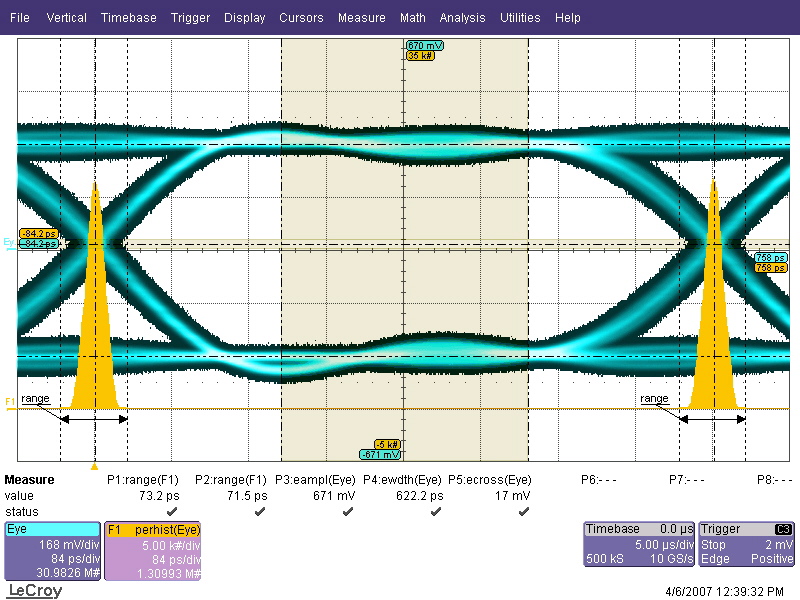

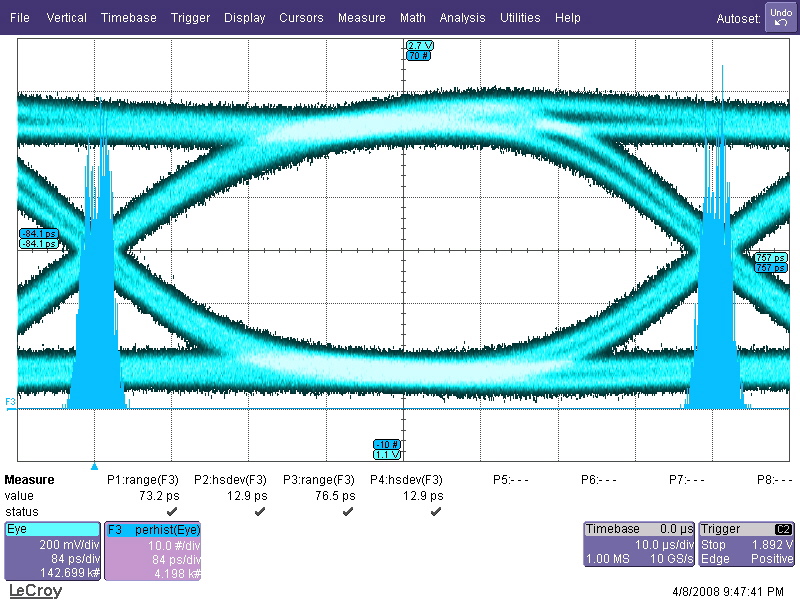

このサイトをオープンしたときにご報告した、1.5Gbps高速シリアル信号回路のデバッグが終了しました。

残念ながら詳細な回路動作に関しては、クライアント様との守秘義務があるので話せませんが、なんとかクライアント様を満足させることができました。

ポイントは、

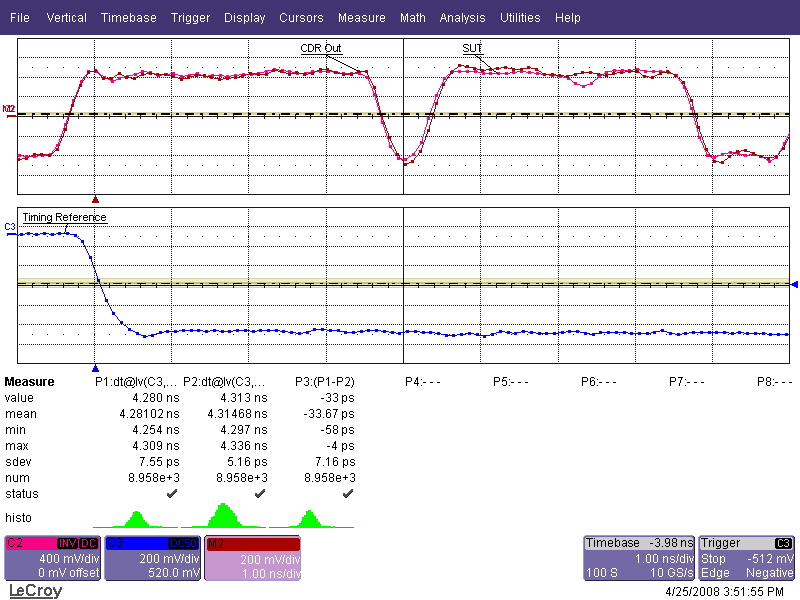

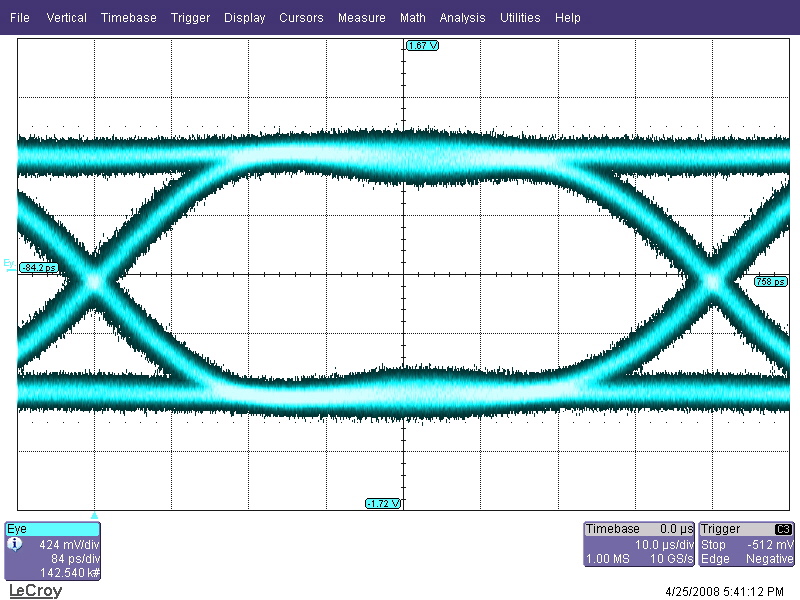

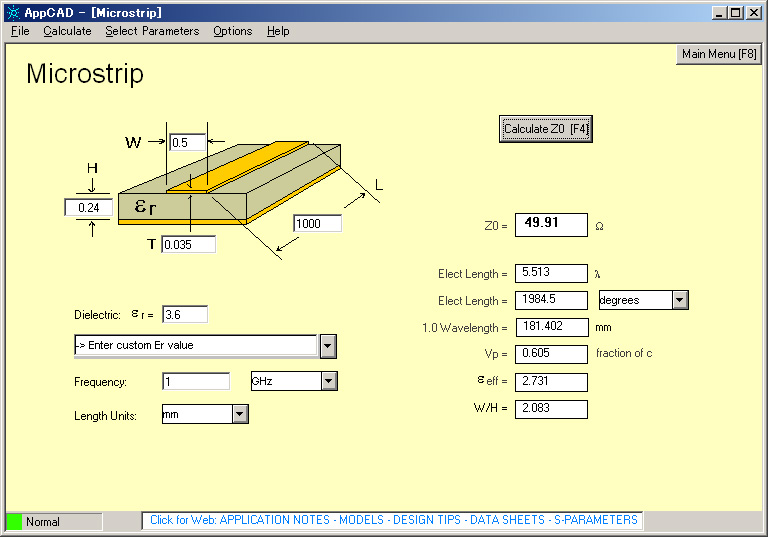

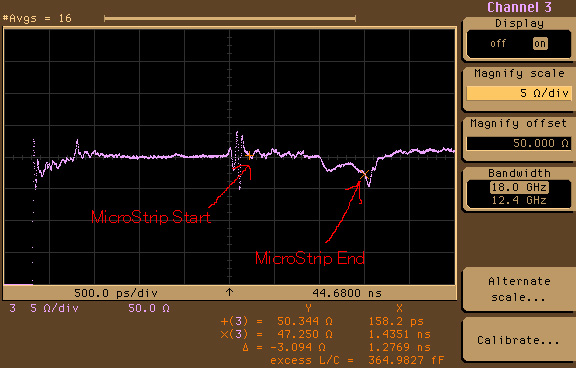

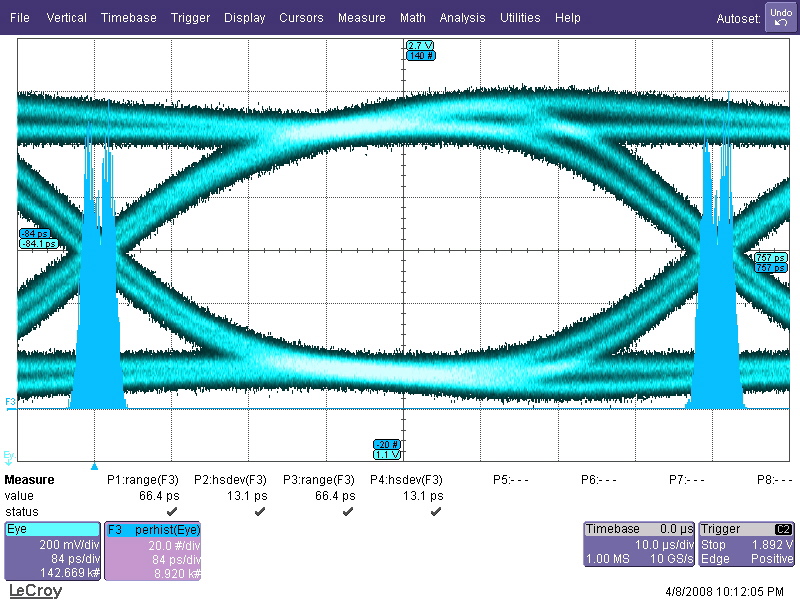

- マイクロストリップラインのインピーダンスが50Ωからずれると、ISIの発生原因になる

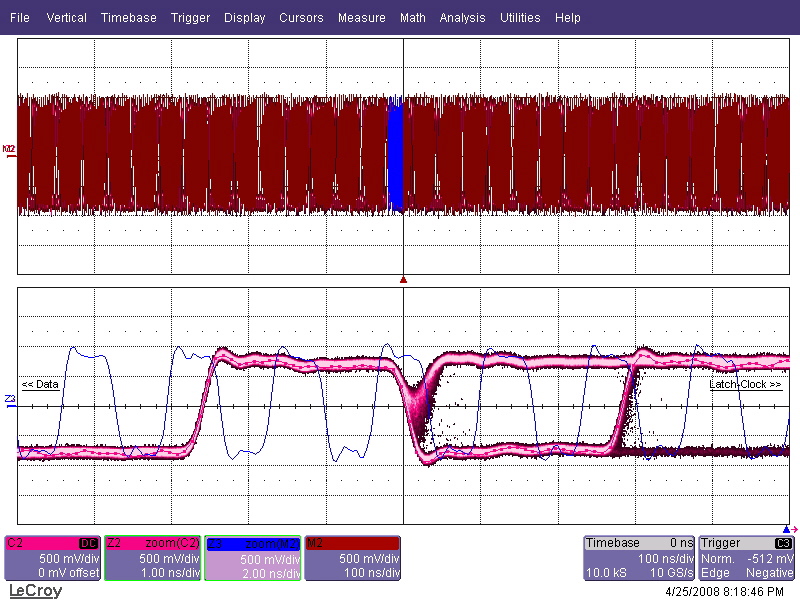

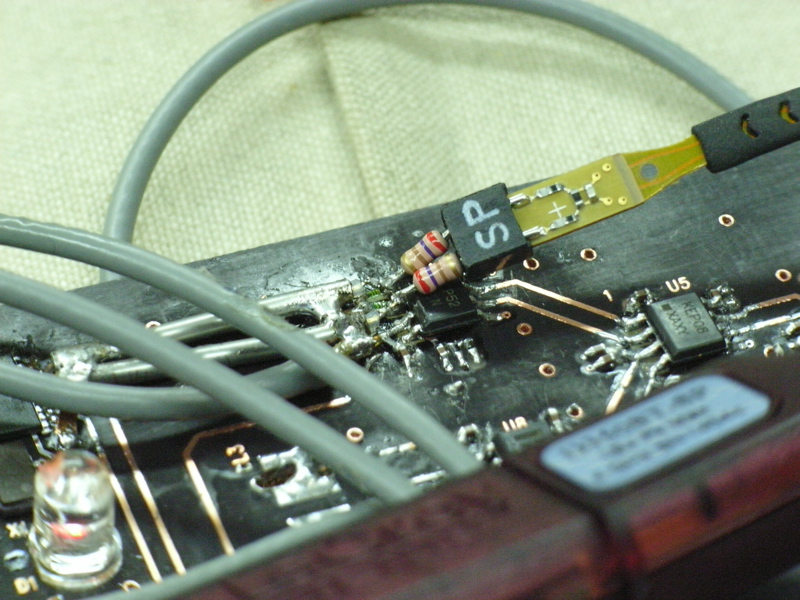

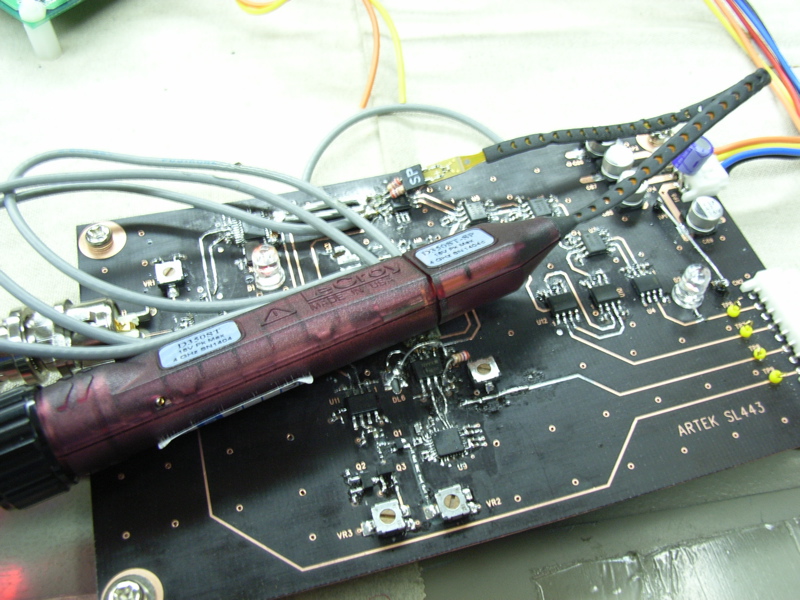

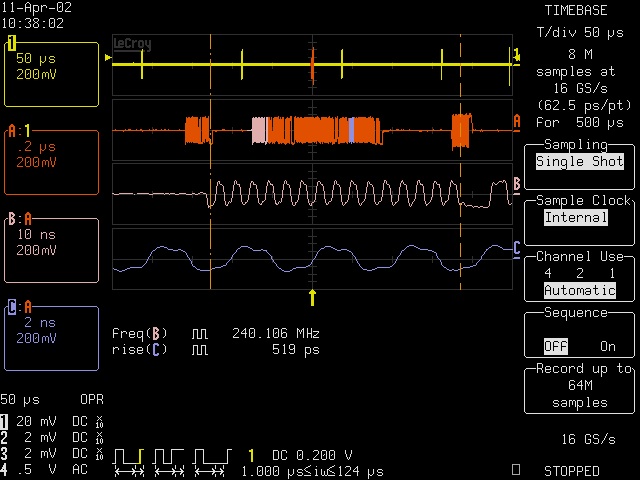

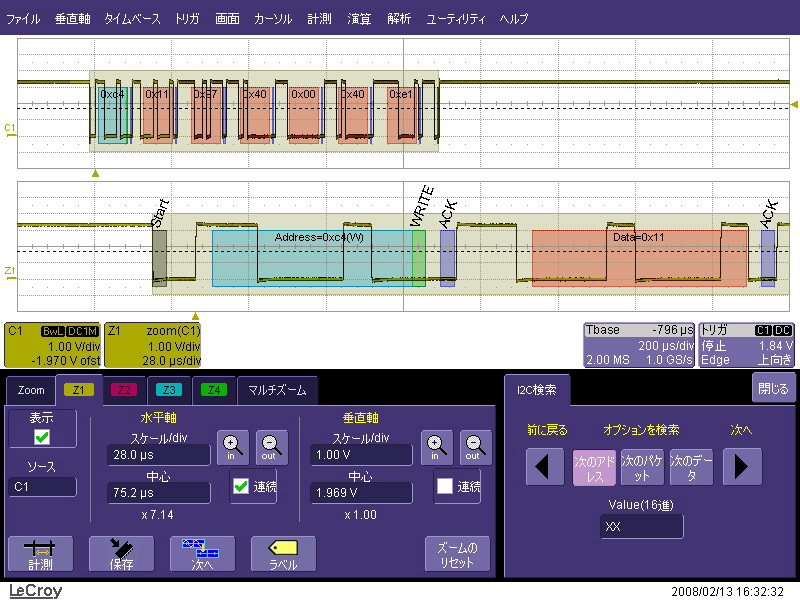

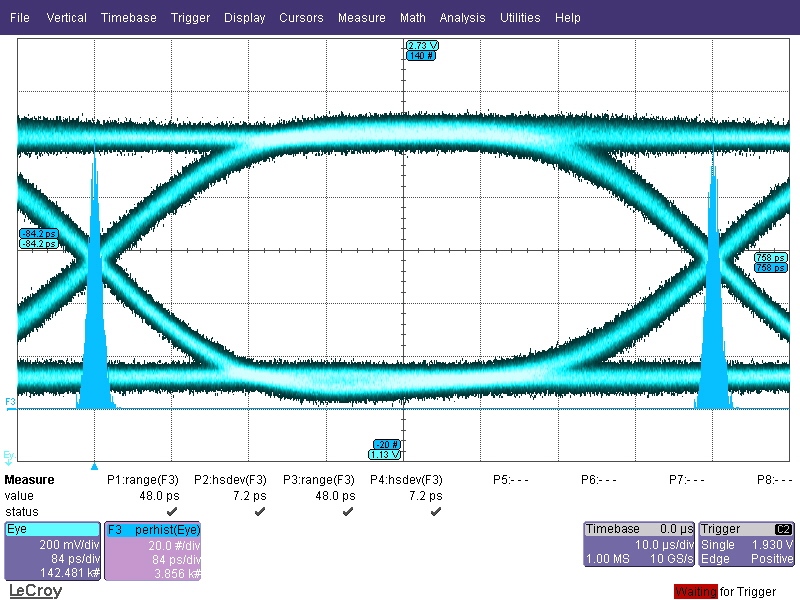

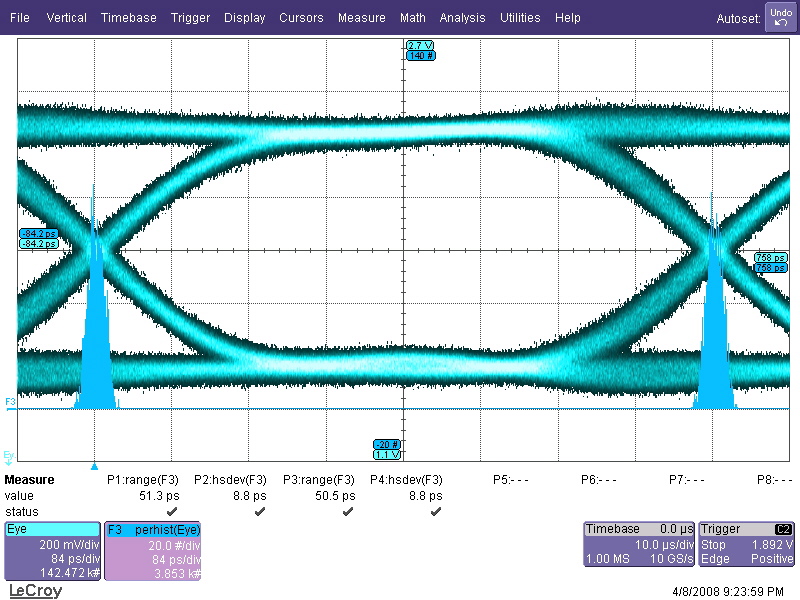

- 波形観測時、半田付けプローブを使うことによって、波形観測の信頼性が格段に上がる

でしょうか?

特に半田付けプローブ強力なツールとなりました。

この場を借りて、半田付けプローブ、D350STを快く貸し出していただいた、レクロイジャパン株式会社 (現テレダイン・レクロイ・ジャパン)様に厚く御礼申し上げます。

詳細に関しては、以下のエントリーを参照ください。

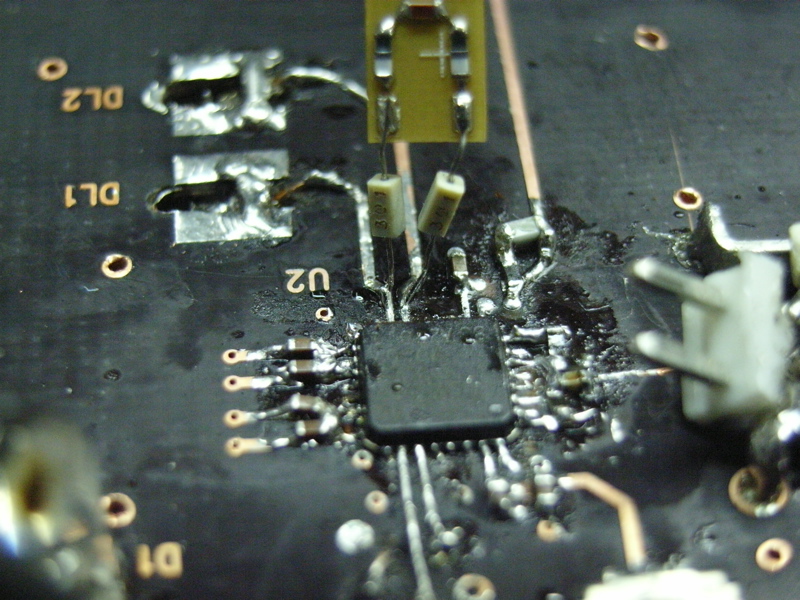

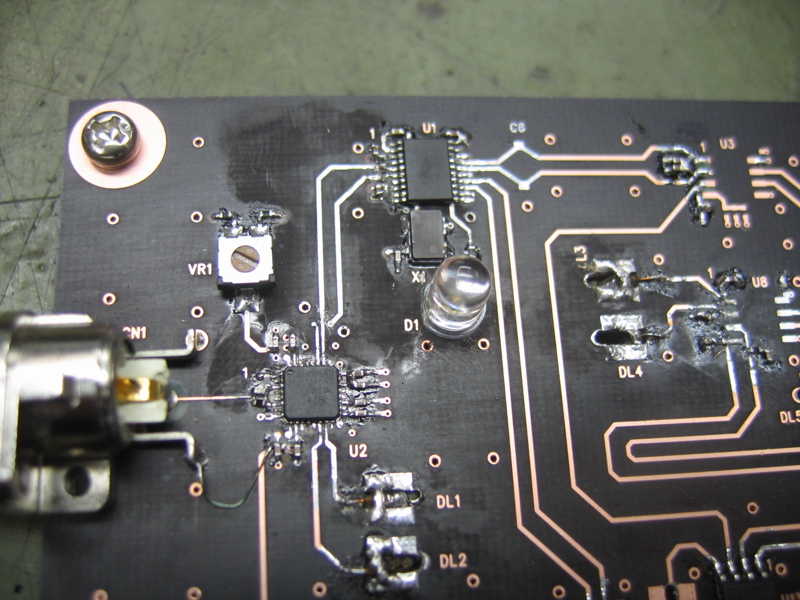

再製作したプリント基板のMicrostrip Lineは50オーム

半田付けプローブを使ってデバッグを行う(Part 1)

半田付けプローブを使ってデバッグを行う(Part 2)

半田付けプローブで観測した波形