前回は、とりあえず中間にビアがあって、第1層から第4層へと変わるマイクロストリップラインの特性を、Genesysを使ってシミュレーションするための方法を示しました。

実はこのやり方は、私が参加したアジレントテクノロジー様主催の

ジレントEEsof EDA フォーラム2008でお会いした、Genesys専任のアプリケーションエンジニアに教えていただいた方法です。フォーラム参加時、お互いに時間があったので、そのアプリケーションエンジニアの方に別室で手取り足取り教えていただきました。

アジレントのUさん、本当にありがとうございました。

これからの目標は、この形状をひな形にして、前回見られた共振点を無くし、リーズナブルな特性を持つマイクロストリップラインの形状を見つける事とします。

まず考えるべきは、なぜこのような共振点が出来たかです。

最も考えられるのは、ビアの部分が分布定数回路ではなく、集中定数回路部品、すなわちインダクタンス成分にみえている、ということでしょう。

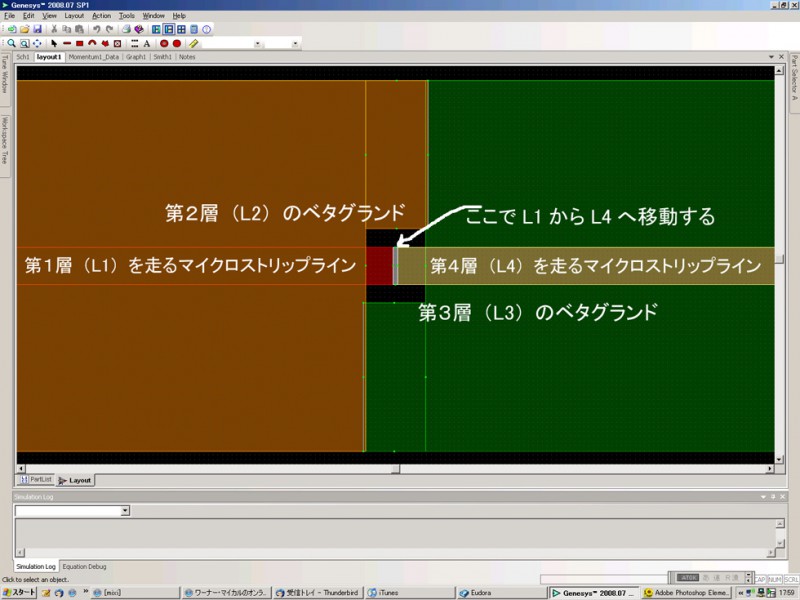

前回の図(図1として再掲)ビアの部分の金属(グランド)の抜きが多いように感じます。つまり、分布定数回路をミクロでみると、小さなインダクタンスが直列に接続され、そのインダクタンスとグランド間にキャパシタンスが並んでいるということになっているのですが、この構造が大きく崩れているのではないか、と考えました。

図1 最初のシミュレーションの形状 マイクロストリップラインとグランドの間隙は0.2mm

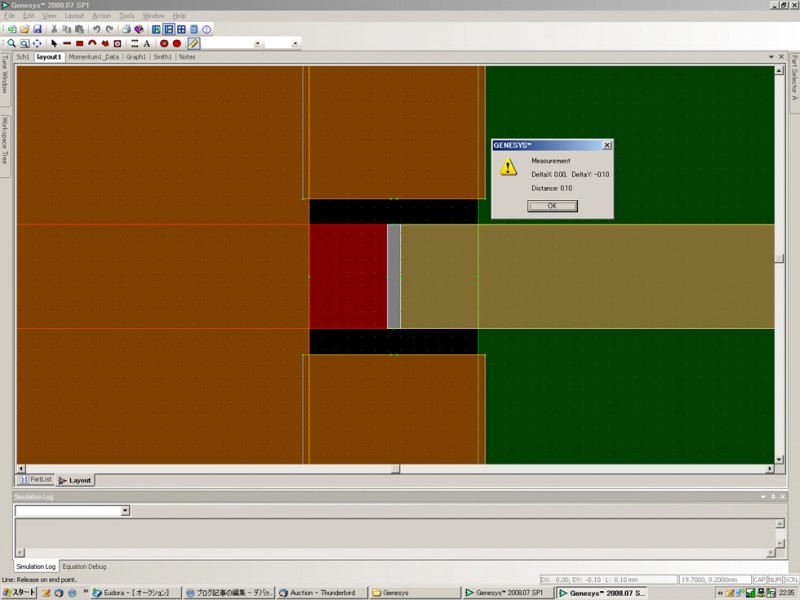

そこで、伝送線路とグランド間のキャパシタンス成分を増やして、集中定数回路的にみえるようにするため、ビア部分のマイクロストリップラインとグランド間の距離を、0.2mmから、0.1mmにしてみました(図2)

図2 マイクロストリップラインとグランドの間隔を0.1mmにした

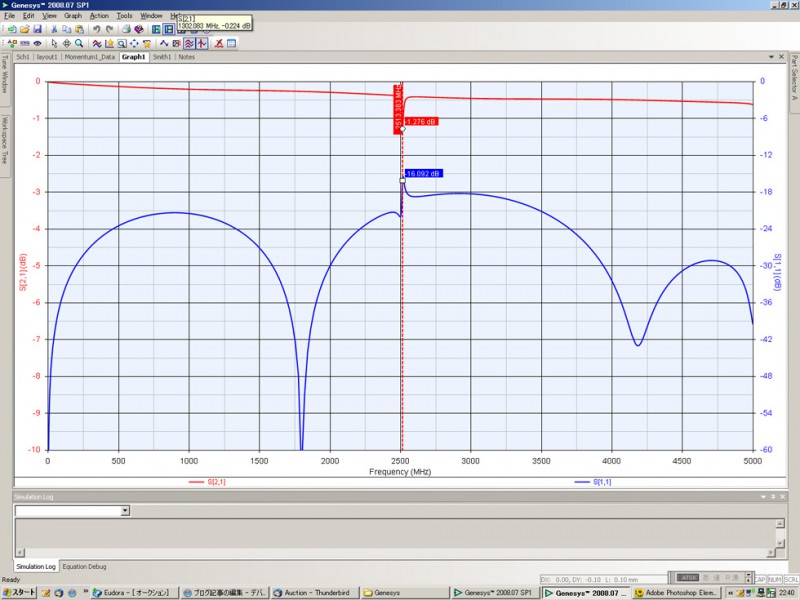

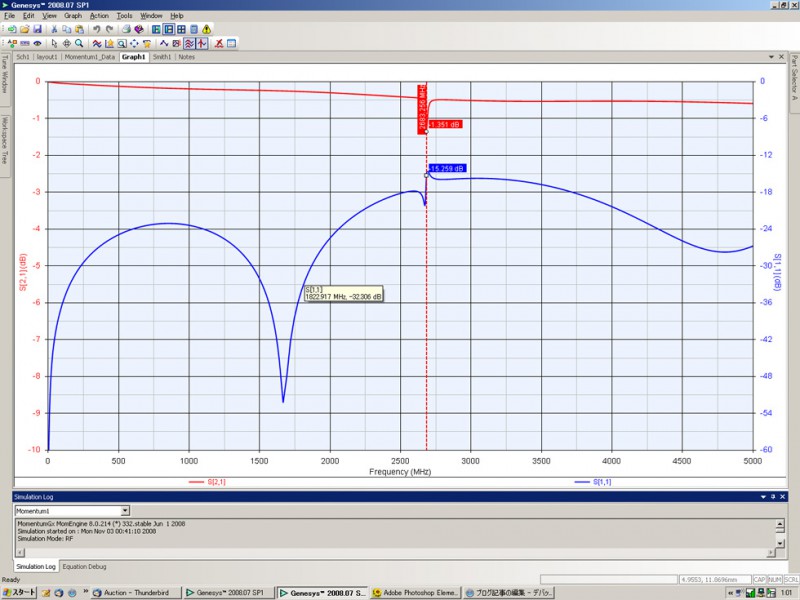

その時のSパラメータが図3です。

図3 図2の形状時のSパラメーター

やはり2.5GHz付近に共振点はあるものの、S21のデータが若干よくなり、S11は共振点における値はあまり変化はないものの、全体的に良い方向(値が小さくなっている)に向かっています。

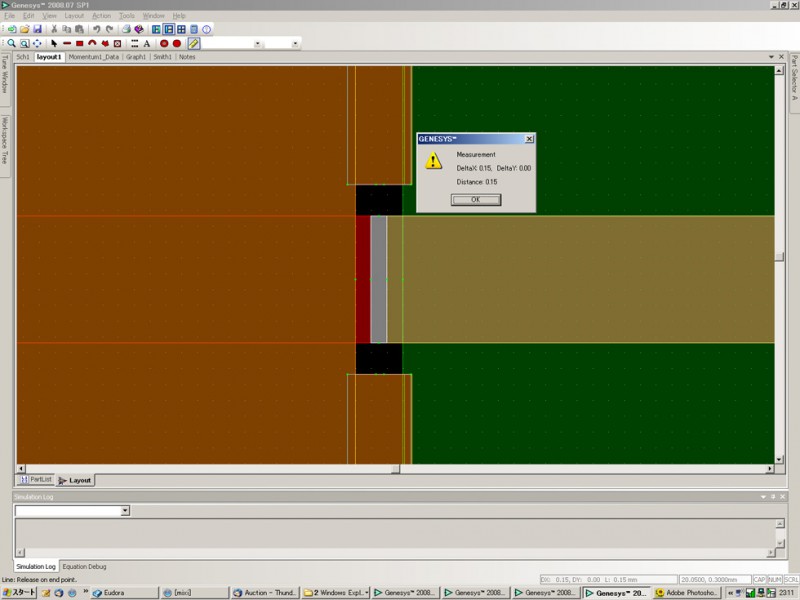

そこで、縦方向だけでなく、横方向のギャップも狭くしてみたらどうなるかシミュレーションすることにしました。

0.65mmのギャップを0.15mmまで狭くしてみたのです。その時の形状が、図4です。

図4 ギャップを0.15mm x 0.1mmとした

図4の形状でシミュレーションを行った結果が図5です。

図5 共振点が高い周波数に移動したがあまり改善は無かった

共振点は高いところに移動したものの、残念ながら良い結果は得られませんでした。その後、いろいろとギャップを変えてみたのですが、あまり良い結果が得られません。とにかく共振点が消えないのです。

そこで、シミュレーションに使っているモデルを考え直すことにしました。特に、今回のモデルの場合は、計算時間を高速にするため、L1の下にあるのは、誘電体層とL2だけで、その下の誘電体層やL3は無いことになっています。L4層も同様です。

ビアの部分は、全ての層を横断するわけですから、全ての金属層及び誘電体層の影響があるはずです。

最終的にモデルを作り直すことにしました。