4月初旬にできあがってきたププリント基板のマイクロストリップラインのインピーダンスが指定の50Ωではなく、57Ωになっていた件ですが、再度プリント基板メーカーに以下の条件で作り直させたところ、マイクロストリップラインのインピーダンスが50Ωになってできあがってきました。

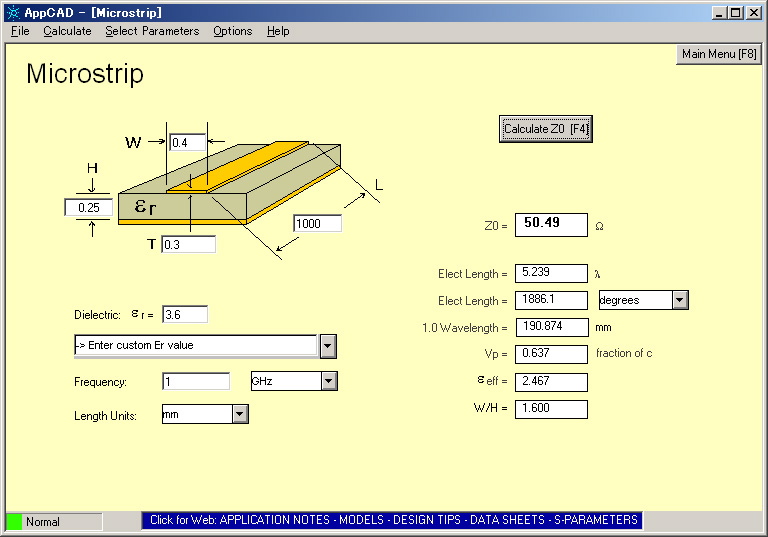

その条件とは、

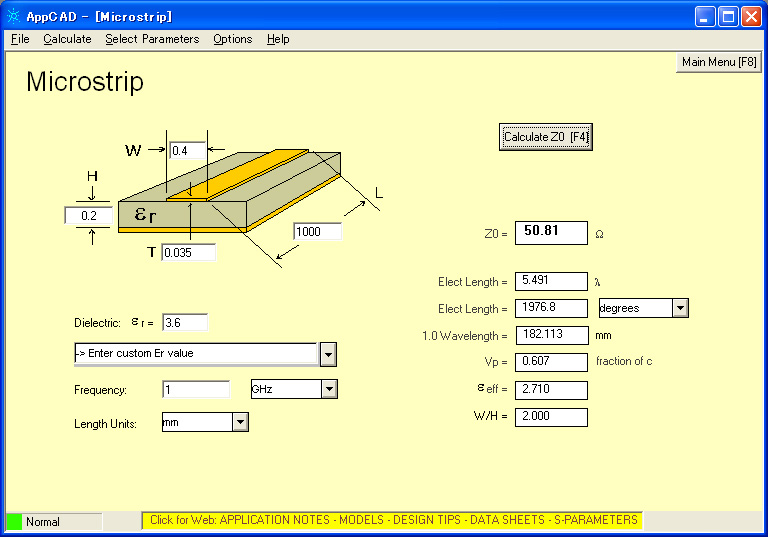

- メーカー曰く、プリプレグの厚みは大きく変動しないとの事であったが、接着や熱をかけてのプレスをすることから考えて、厚みはある程度変動すると考えた。そのため、プリプレグの厚み指定は前回と同じ0.2mm。

- マイクロストリップラインの幅は、ある程度コントロールされていて、幅の変動はほとんど無視できるとした。

- プリプレグの誘電率も、同じメーカーで作るのであれば変わらないと考えて、3.6を採用。

- 結局、前回のプリント基板では、製造段階でプリプレグの厚みが変わったと判断。マイクロストリップライン幅を0.4mmから0.5mmに変更した。

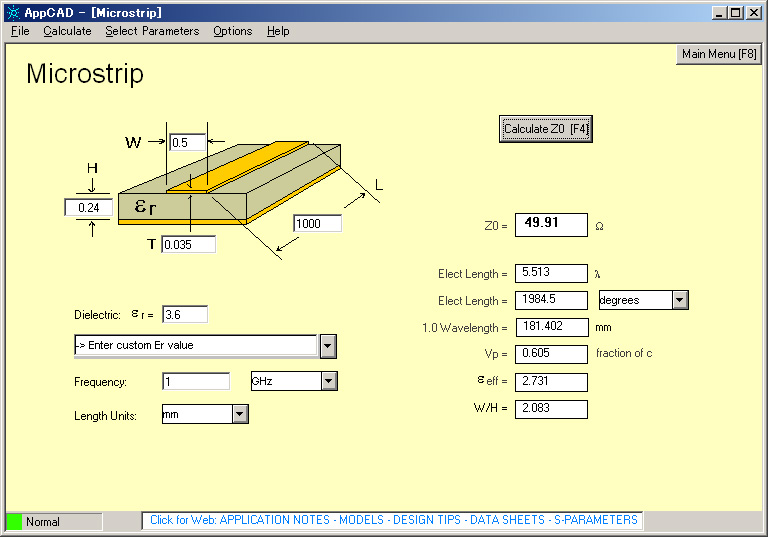

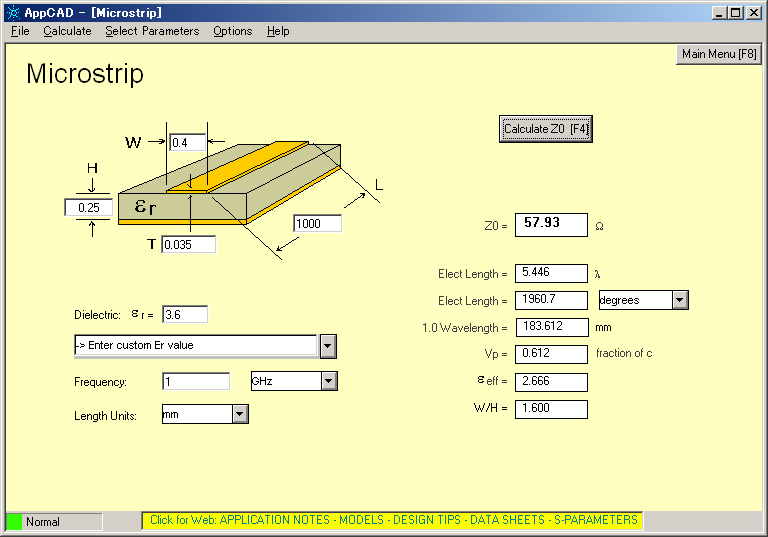

この条件を、アジレントテクノロジー社アバゴテクノロジー社のAppCADに入れたときの結果が以下の図です。

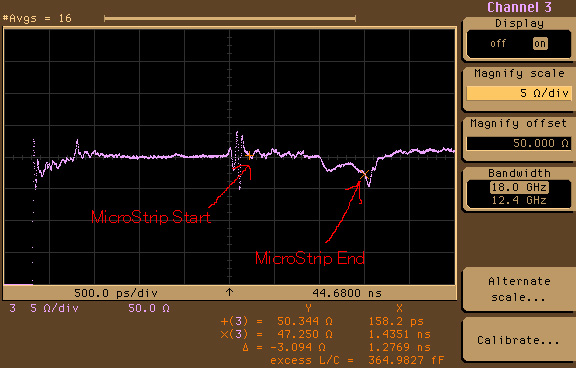

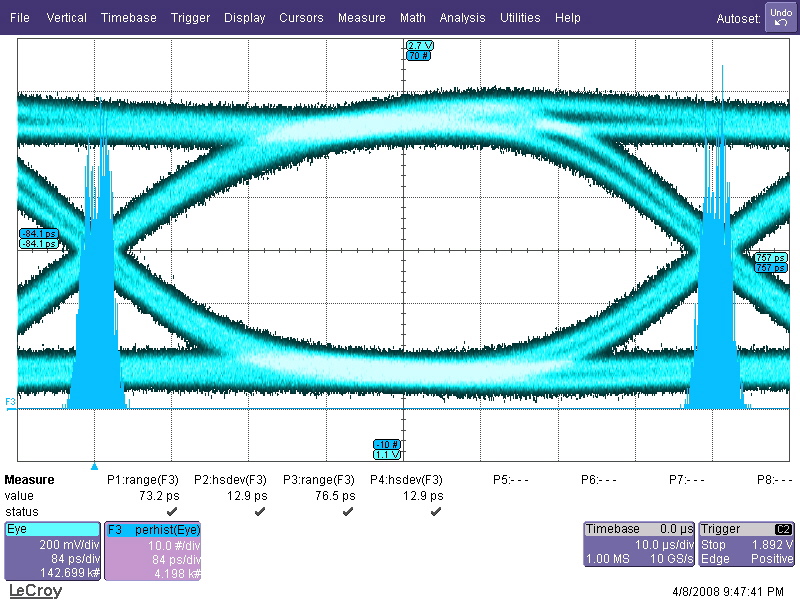

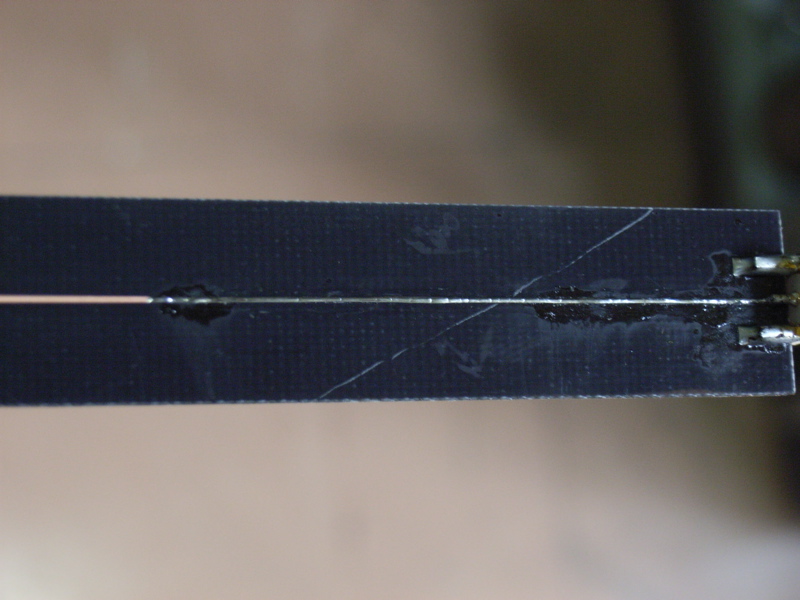

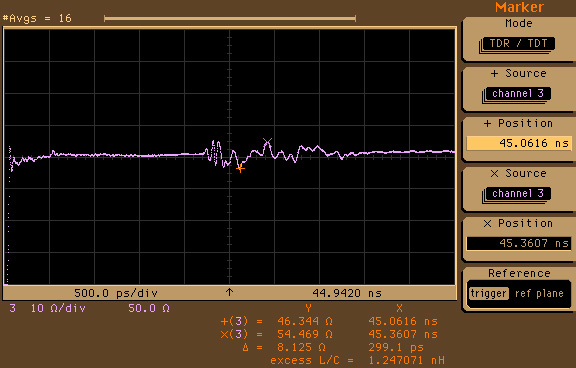

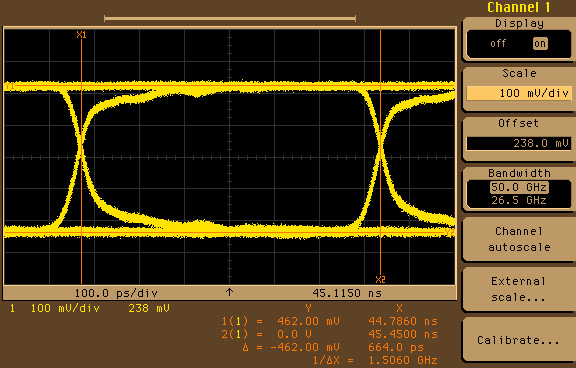

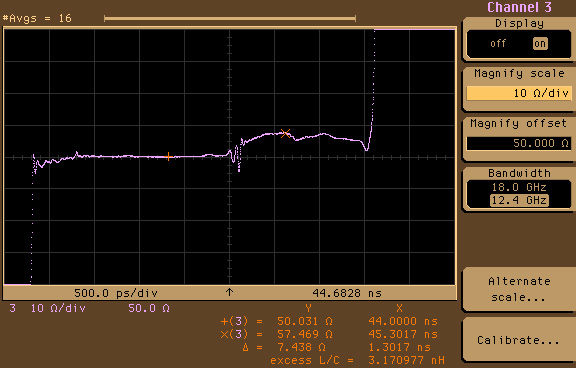

エンド部分手前のへこみが気になりますが、ちゃんと50Ωになったテストクーポンができあがってきました。これなら問題ありません。

再度プリント基板メーカーに確認したところ、前回製作した時と製造方法も材料も、さらに層構成も全く同じとのこと。

やはり、製造段階でプリプレグの厚みが変化したものと考えざるを得ません。理由が不明なのが残念ですが・・・

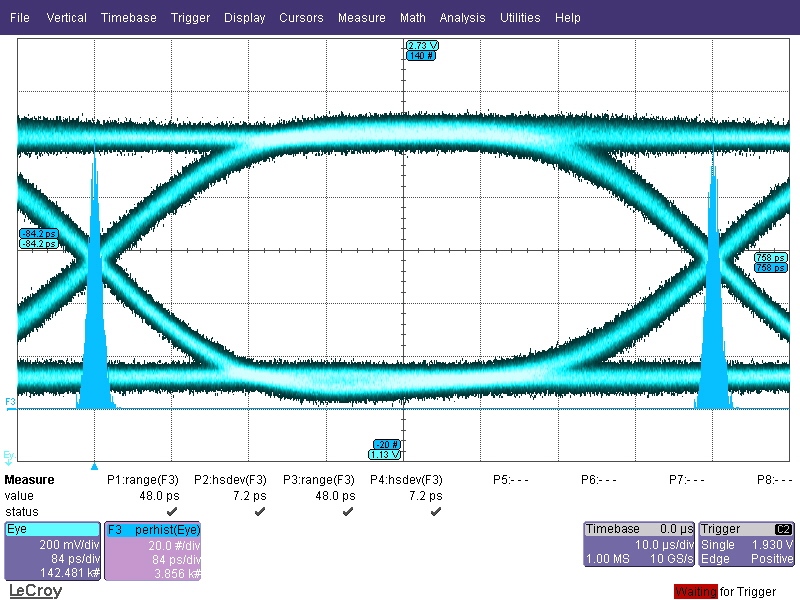

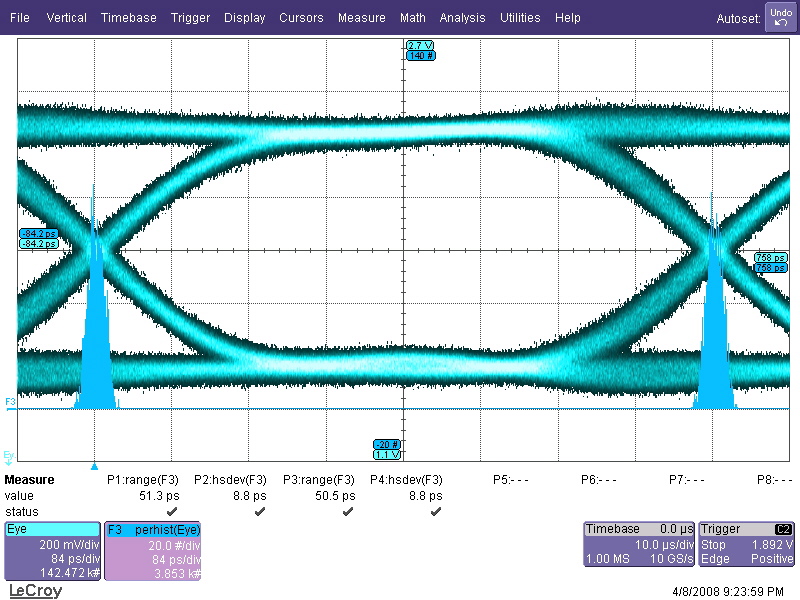

ともあれ、マイクロストリップラインのインピーダンスの問題は片付きました。あとは動作の確認をするのみです。