皆様、おはようございます。

デバッグ・ラボ 代表、國頭延行が翻訳を手がけました、

にて、70位〜30位あたりをウロウロしていたのですが、ここ一週間ほどは、20位から10位の間で推移しております。本日午前7時現在、14位です。

これほど売れるとは思っていませんでしたので、第一刷の印刷部数は少ないのです。この機会に、在庫の無くなる前に、早めのご購入をお勧めします。

皆様、おはようございます。

デバッグ・ラボ 代表、國頭延行が翻訳を手がけました、

これほど売れるとは思っていませんでしたので、第一刷の印刷部数は少ないのです。この機会に、在庫の無くなる前に、早めのご購入をお勧めします。

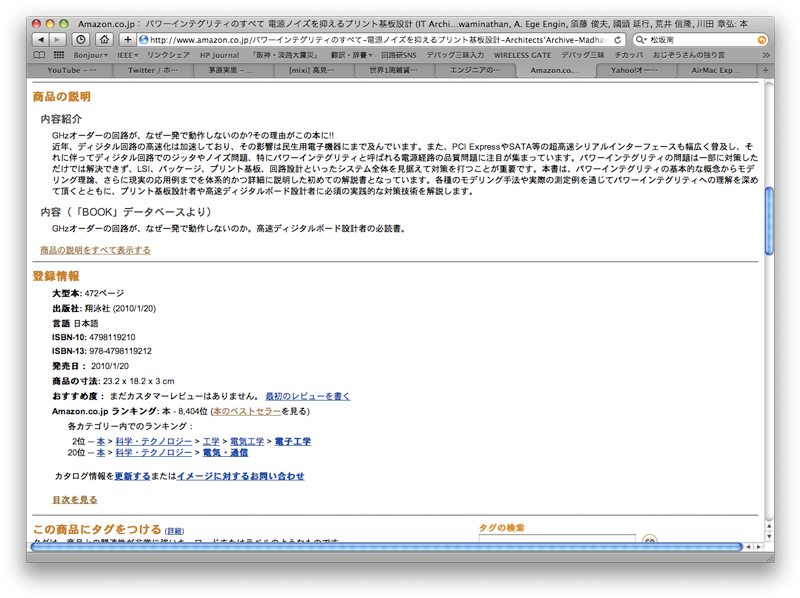

さて、前のページでご紹介した、「パワーインテグリティのすべて」には、原著の著作者である、アメリカ、ジョージア工科大学の、Dr.Madhavan Swaminathan(マドハバン・スワミナサン博士)から、日本語版への序文を頂きました。その一部をここに紹介し、全文は、PDFとしてここに置いておきます。

この本は、2007年にアメリカで発行された、Power Integrity Modeling and Design for Semiconductors and Systemsの翻訳版です。

この本は、2007年にアメリカで発行された、Power Integrity Modeling and Design for Semiconductors and Systemsの翻訳版です。理工書ですので、第一刷はそれほど沢山印刷しておりません。お早めの購入をお勧めいたします。

皆様、明けましておめでとうございます。本年もどうぞ宜しくお願いいたします。

Power Integrity Modeling and Design for Semiconductors and Systems

6月9日に「ハワード・ジョンション博士(Dr. Howard Johnson)のアプリケーションノートの翻訳が好評、との新着情報を書きましたが、折角なので、今までやってきた翻訳の例を引いて、翻訳時の苦労話を連載で書きたいと思います。

2015年9月22日追記:

記事の後半部分が失われてしまっています。恐らく2014年末にホスティング会社を変えた時に何か起こったようです。復帰次第、最新情報でお知らせしますので、暫くお待ち頂ければ幸いです。

現在、レクロイ・ジャパン様(現:テレダイン・レクロイ・ジャパン様)向けに、シグナル・インテグリティ分野のパイオニアである、ハワード・ジョンション博士(Dr. Howard Johnson)が書かれているアプリケーションノート「Fundamentasl of Signal Integrity」を翻訳させていただいています。

「最新情報」にも少し書きましたが、「Fundamentals of Signal Integrity」の翻訳版である、「シグナル・インテグリティ基本」が発行された、というE-mail配信があると、レクロイ・ジャパン様のWEBサーバーへのアクセスが、最大で通常の5倍まで増えたとか・・・

最初にお金を頂いて翻訳をしたのは、CQ出版社から発行されてる「アナログ・テクノロジシリーズ OPアンプ大全」でした。原本はアナログデバイセズ社が発行している「OP Amp Applications」と呼ばれる1000ページ以上はある本です。当然ながら私一人では出来ませんから、CQ出版社の著者の会である「電子回路技術研究会」のメンバーの内約10名程で翻訳を始めました。

現在、アメリカのデジタルオシロスコープメーカー、レクロイ社が(現:テレダイン・レクロイ社)2008年6月から発行している、「Fundamental of Signal Integrity」の翻訳を続けさせていただいております。

トランジスタ技術 2009年2月号と3月号に、「位相雑音とジッタの関係を探る」と題して記事を書きました。

11月から続けていた、ビアのあるマイクロストリップラインの特性解析が、本日終了いたしました。